今度はこの本ですよ。前の本の続編ということで、まずはJ-FETからだ。前に、バイポーラやMOS FETでいろいろ遊んだが、そういえばJ-FETはまだだった。2SK30とか2N7000の話の時は、ジャンクションとMOSを一緒に話してたからダメですねw(^^♪

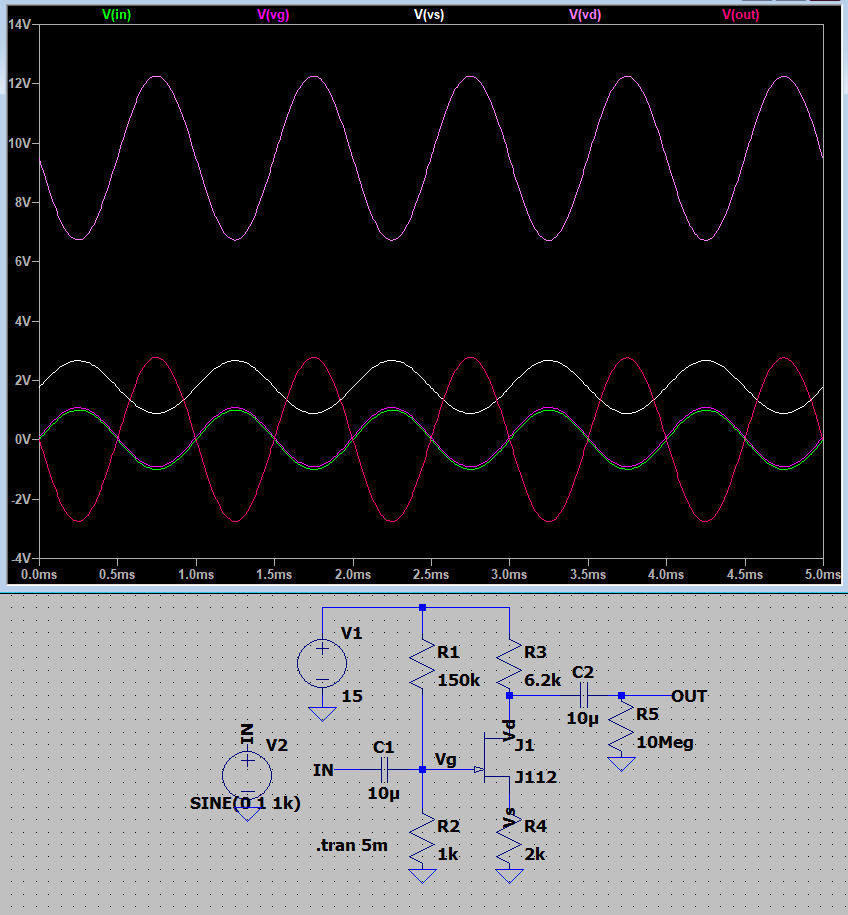

なのでまずは、ソース接地から。42ページ図1をやる。その前に、例によってLTspice上で何を選ぶかという問題。J112を選びました。「安い」「秋月で買える」のにLTspiceにあるのでこれに決まりです。で、やってみた。これ。

とりあえず全部の場所の電圧を測定。入力振幅は1Vなので、いろいろ飽和しまくってますね。

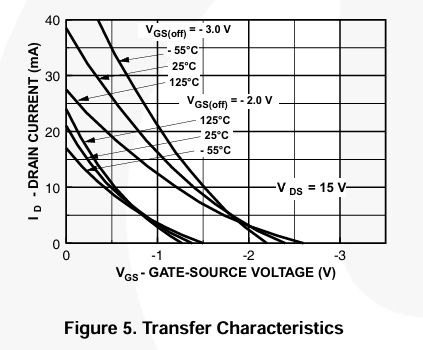

J112のデータシート抜粋はこれ。

最初はちょっとびっくりするけど、昔の日本の本やデータシートと違って、現代ではこういうふうにVGSのマイナス電圧を横軸にして書くんですね。どう見てもデプレッション型で、昔懐かしいJ-FETそのものになってます。デプレッションでJ-FET なのを見ないとなんか安心しない…という変な病気がwww(^^♪ これもなかなか通じなさそうなネタですが・・・・(^_-)-☆

ちゃんとVGSがマイナス1~2Vあたりで動作してるので、さっきのカラーのグラフの、濃いピンク色の線よりも、白い線のほうが、同相で1.5V位高くなってますね。そのかわり、しっかり上がクリップしてますが(^^♪

45ページの11式から、電圧増幅度はRd/Rsなので、3倍ということに。

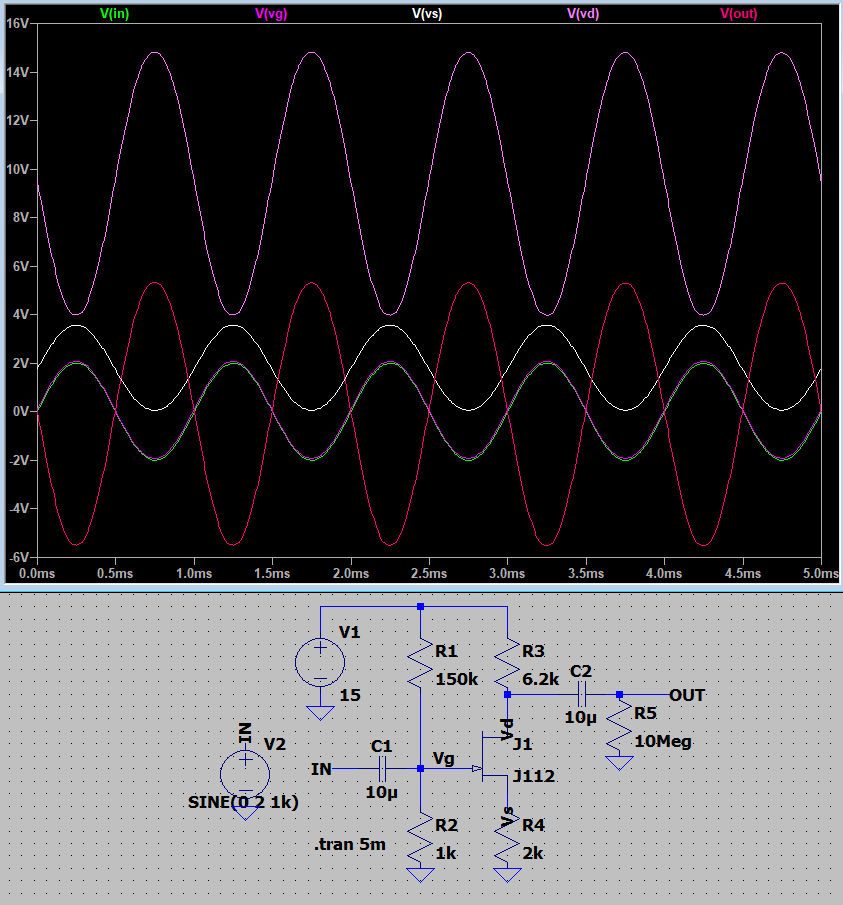

なので、ゲートバイアスをいじってクリップを無くて行きますが、やった結果はこれ。

R2を1kΩにしたところ、いい感じになりました。これならこのように、

入力振幅を2Vにしても、歪まずに約6V弱の出力が出てますね。では次はf特。これ。

赤い線を見ると、10MHzくらいまで伸びてます。いいのではないでしょうか。成功だ。

コメント