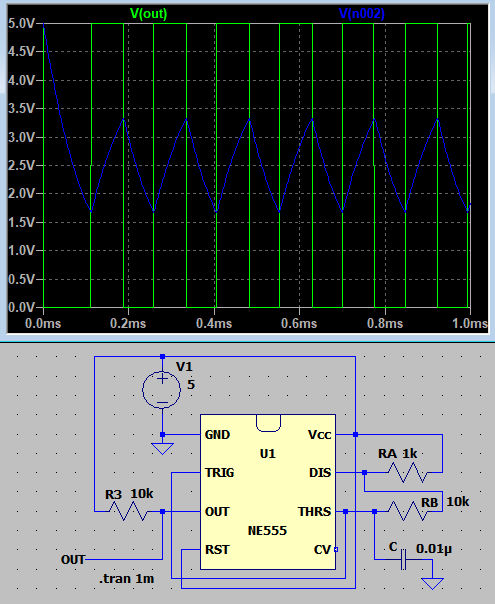

この本の81ページの図22。あの555がちゃんと載っているし、もっと驚異なのはLTspiceにも標準装備であることだ。こういうふうにいろんなICがちゃんと揃っていればLTspiceはもっと使いやすくなるのに・・・でも宣伝用無料ソフトなのでそれは無理だろう。こういうの、廉価有料版で、そういうニーズを満たしたのを作ればいいのに。。。な~んて、買う人がいないんだろう(^^♪

やってみた。これ。

さすが専用ICとLTspiceデフォルトで搭載だけあって、一発で成功。

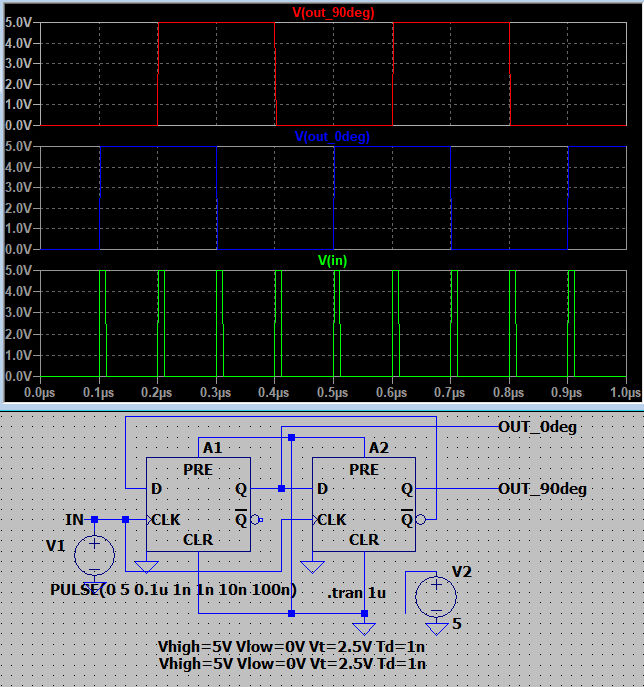

次は、88ページの図27、2相クロック発生回路。これ。

見ての通りなので一発で成功するかと思いきや・・・ダメだったので、最初は無かった電源電圧5V設定&CLR・PRE端子プルアップなどもやってみたが、やはりダメは変わらず。なんで??

いろいろやった結果、このようにうまくいった。

CLR・PREがなぜか正論理になっているので、ちゃんとGNDに配線したり、Vtを入れたりもあったのだが、本質的に原因となったのが、Td=1nを入れたこと。

これは、最初のDFFの動作を考えれば当たり前なのだが、もしTdが0だと、2個目のDFFのQの否定の電圧と1個目のDFFのDの電圧が同一のタイミングで論理1・0になってしまい矛盾が発生してしまう。現実の回路だとちゃんと遅れが発生するので矛盾しないのだが。

というわけで、CLKを4分周した周波数の、90度位相がずれたDuty比50の2つのクロックが得られた。これで第3章が終了した。

コメント